I don't deny that performance seems fine on the drive.

Mine boots fine, loads things fine and plays fine but I'm using rapid which would mask the issue anyway to some degree.

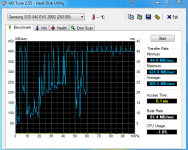

It's not just a benchmark issue though as I have said I see the performance issue when attempting an acronis backup of the drive.

So there is an issue there just not entirely sure what.

It may well be that the drive hand off between dram cache and drive is bad with small files.

It stands to reason that the first section of my drive will have the OS installed on it which will be packed full of tiny files.

Which may well be the issue that the drive read speed for lots of small files is really bad (by design or bug) and that larger files don't exhibit this issue.

Throwing idea's out there.

Please test your drive regardless of whether you think it is fine though. It's not a witch hunt it's trying to understand an issue we have identified and judging how wide an issue it is.

Takes 2 mins to download and run the HDTune benchmark and it's free.

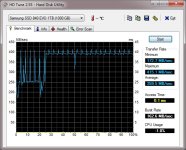

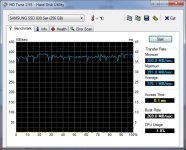

Ultimately a drive's read performance should not be effected by age nor file location on the drive. The drive should be able to read a data block on any nand cell at the same speed regardless of age but as this proves it just isn't happening. i.e reading cell 200 on chip 1 should be equally as fast as cell 1 on chip 4.

Locating the nand cell and then reading the data out should be the same.

As john and I have show we've tested sequential read's here so we are asking it to read cell1,2,3,4 in order which should be faster than asking for random cells but again it's not. It may well be how the data is distributed over cell boundaries or chip boundaries I don't know.

So although the file is sequential on the drive virtually it's not physically sequential and data could be distributed across chips I believe this is how the internal firmware file map would work. You would expect it to write a file across multiple chips to improve read access time as the controller has multiple channels. So faster to read all channels in one cycle rather than having to cycle the same chip to read out of it multiple times.

That may well explain the issue it may well be that samsung's attempt to limit drive wear is forcing small amounts of data to be less well distributed across the chips.

The more I type the more I think this makes sense with my limited understanding of nand and SSD technology.

so it maxes out at SATA2 speeds. My poor read performance is spread more 'widely' across the drive - not just the 'start' (if these terms mean anything on an SSD...

so it maxes out at SATA2 speeds. My poor read performance is spread more 'widely' across the drive - not just the 'start' (if these terms mean anything on an SSD...  )

)