I've pretty much reached the limit of my knowledge about about tuning RAM on a Ryzen system.

For search engines:

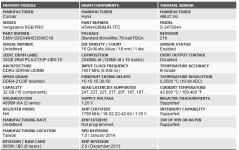

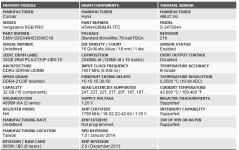

Corsair Vengeance RGB Pro CMW128GX4M4D3600C18

Hynix M-die (MJR) H5ANAG8NMJR-TFC

It's 128G Vengeance Pro 3600 C18-22-22-42 kit, it's Hynix parts but at that density there wasn't really a lot of options in stock without importing and praying.

In any case I understand Hynix has the capacity for higher frequency but depending on the die/bin can suck for tighter timings.

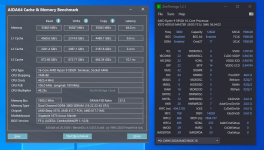

I think I can probably thank my SoC silicon, I pretty much just slapped this stuff in - set the SoC voltage to 1.15v, set the FCLK to 1900 and the RAM to 3800. Booted first go, nice.

It posts at 18-20-20-36 with 1.36v but fails hard at C16 at any frequency (this was expected after reading about Hynix M die).

Are there any more easy sub timings I should tighten up? I really have no clue what to look at next, thinking there's probably not much room for improvements now?

For search engines:

Corsair Vengeance RGB Pro CMW128GX4M4D3600C18

Hynix M-die (MJR) H5ANAG8NMJR-TFC

It's 128G Vengeance Pro 3600 C18-22-22-42 kit, it's Hynix parts but at that density there wasn't really a lot of options in stock without importing and praying.

In any case I understand Hynix has the capacity for higher frequency but depending on the die/bin can suck for tighter timings.

I think I can probably thank my SoC silicon, I pretty much just slapped this stuff in - set the SoC voltage to 1.15v, set the FCLK to 1900 and the RAM to 3800. Booted first go, nice.

It posts at 18-20-20-36 with 1.36v but fails hard at C16 at any frequency (this was expected after reading about Hynix M die).

Are there any more easy sub timings I should tighten up? I really have no clue what to look at next, thinking there's probably not much room for improvements now?

Last edited:

. It's latency improvements you'll feel most in usage, so that's where you want to spend most of your efforts really. Its the rarer use cases where bandwidth comes to the fore...though 4 x 32gb is a rare use case already

. It's latency improvements you'll feel most in usage, so that's where you want to spend most of your efforts really. Its the rarer use cases where bandwidth comes to the fore...though 4 x 32gb is a rare use case already