It's about time we had some more photos

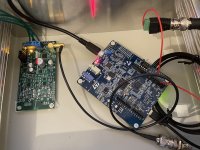

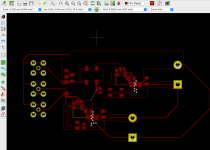

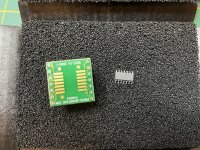

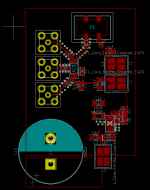

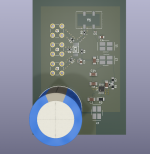

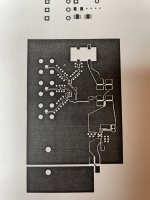

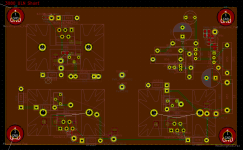

Board to the left - ADC board to the right STM32F23 discovery board.

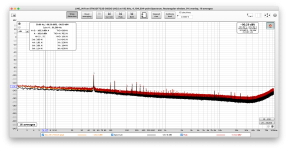

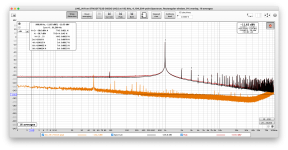

I now have the STM appearing as a high speed USB Audio 2.0 device, capable of 192+KHz 32bit. Although in linux it seems happy the Mac seems to have issues at the moment.. so I use a RPI4 to act as the USB host

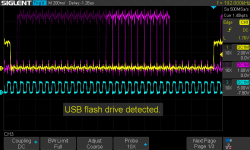

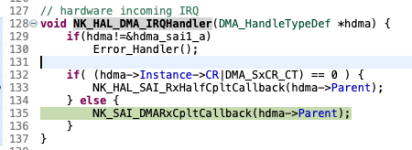

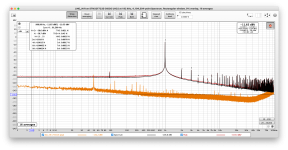

I've found my connection between the board isn't working well at the moment so I'm using a direct signal generator to create the signal for the STM's Serial Audio Interface (SAI) to lock onto (it's i2S/PCM) by using the signal generator channels to clock the bit clock and the frame clock (at 1/2 speed). This seems to work as I now get a interrupt and DMA for the SAI input:

Once this is working, the STM will act like a bridge so that the ADC card will appear like a USB Audio microphone

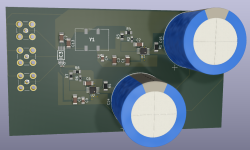

I've got the bits to make this and use the bench power supplies, including a scaling divider resistors so that it will take up to 400V peak to peak which will be useful for tube amps. I also bought a metal case so it will be shielded eventually.

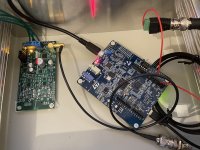

Board to the left - ADC board to the right STM32F23 discovery board.

I now have the STM appearing as a high speed USB Audio 2.0 device, capable of 192+KHz 32bit. Although in linux it seems happy the Mac seems to have issues at the moment.. so I use a RPI4 to act as the USB host

I've found my connection between the board isn't working well at the moment so I'm using a direct signal generator to create the signal for the STM's Serial Audio Interface (SAI) to lock onto (it's i2S/PCM) by using the signal generator channels to clock the bit clock and the frame clock (at 1/2 speed). This seems to work as I now get a interrupt and DMA for the SAI input:

Once this is working, the STM will act like a bridge so that the ADC card will appear like a USB Audio microphone

I've got the bits to make this and use the bench power supplies, including a scaling divider resistors so that it will take up to 400V peak to peak which will be useful for tube amps. I also bought a metal case so it will be shielded eventually.

Last edited:

a Duracell battery or two in stack! The system will not use the power but it will use the voltage to maintain a negative rail. That way the VP p-channel mosfet that is there to help the auto balance of the system should work better

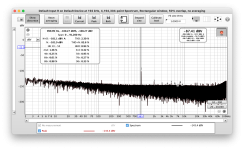

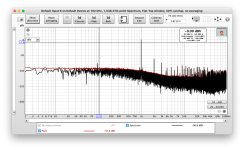

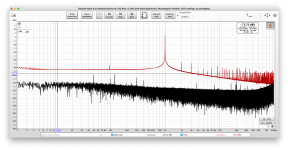

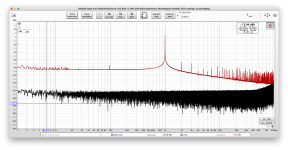

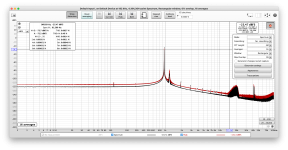

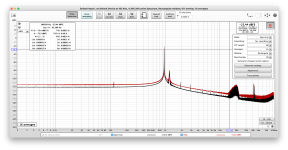

a Duracell battery or two in stack! The system will not use the power but it will use the voltage to maintain a negative rail. That way the VP p-channel mosfet that is there to help the auto balance of the system should work better  how's how much noise having the extension cable on the desk gives!

how's how much noise having the extension cable on the desk gives!

so the Idea is to finish this as much as I can so things don't get lost etc.

so the Idea is to finish this as much as I can so things don't get lost etc.