tl:dr DDR5 will launch at 4800mhz and 1.2v

https://videocardz.com/press-release/jedec-publishes-new-jesd79-5-high-performance-ddr5-standard

https://videocardz.com/press-release/jedec-publishes-new-jesd79-5-high-performance-ddr5-standard

ARLINGTON, Va., USA – JULY 14, 2020 – JEDEC Solid State Technology Association, the global leader in the development of standards for the microelectronics industry, today announced the publication of the widely-anticipated JESD79-5 DDR5 SDRAM standard. The standard addresses demand requirements being driven by intensive cloud and enterprise data center applications, providing developers with twice the performance and much improved power efficiency. JESD79-5 DDR5 is now available for download from the JEDEC website.

DDR5 was designed to meet increasing needs for efficient performance in a wide range of applications including client systems and high-performance servers. DDR5 incorporates memory technology that leverages and extends industry know-how and experience developing previous DDR memories. The standard is architected to enable scaling memory performance without degrading channel efficiency at higher speeds, which has been achieved by doubling the burst-length to BL16 and bank-count to 32 from 16. This revolutionary architecture provides better channel efficiency and higher application level performance that will enable the continued evolution of next-generation computing systems. In addition, the DDR5 DIMM has two 40-bit fully independent sub-channels on the same module for efficiency and improved reliability.

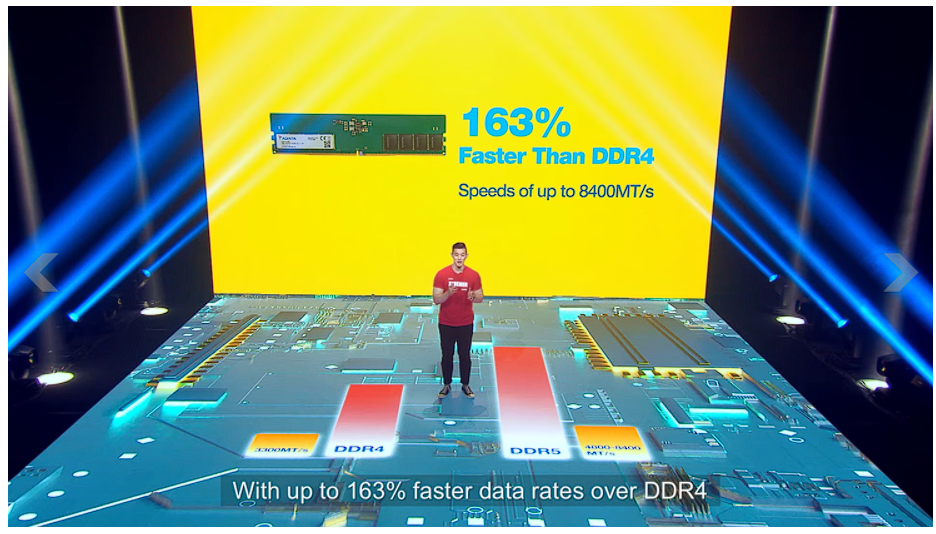

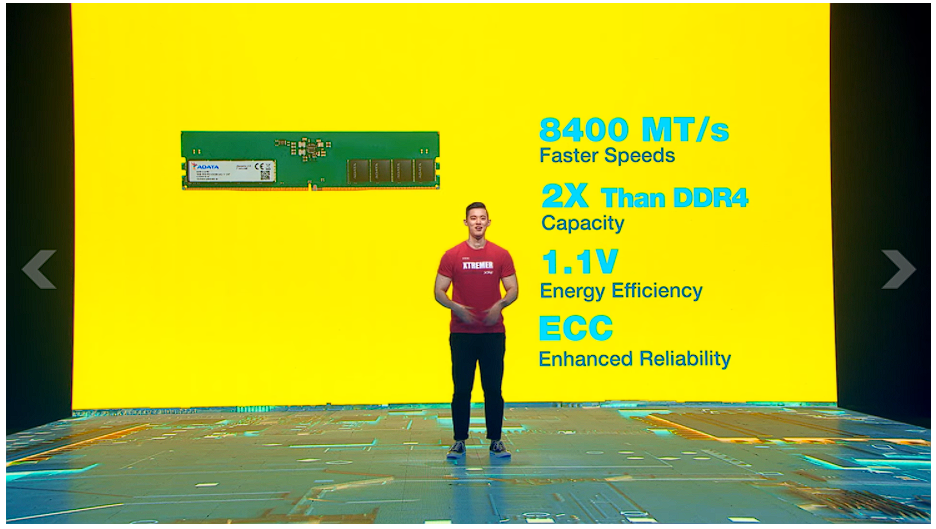

New features, such as DFE (Decision Feedback Equalization), enable IO speed scalability for higher bandwidth and improved performance. DDR5 supports double the bandwidth as compared to its predecessor, DDR4, and will be launched at 4.8 Gbps (50% higher than DDR4’s end of life speed of 3.2 Gbps).

Additional features include:

- Fine grain refresh feature: as compared to DDR4 all bank refresh improves 16 Gbps device latency. Same bank selfrefresh offers better performance by enabling some banks to refresh while others are in use.

- On-die ECC and other scaling features enable manufacturing on advanced process nodes.

Improved power efficiency enabled by Vdd going from 1.2V to 1.1V as compared to DDR4.- Use of the MIPIÒ Alliance I3C Basic specification for system management bus.

- At the module level, voltage regulator on DIMM design enables pay as you go scalability, better voltage tolerance for improved DRAM yields and the potential to further reduce power consumption.

- “With several new performance, reliability and power saving modes implemented in its design, DDR5 is ready to support and enable next-generation technologies,” said Desi Rhoden, Chairman JC-42 Memory Committee and Executive VP Montage Technology. “The tremendous dedication and effort on the part of more than 150 JEDEC member companies worldwide has resulted in a standard that addresses all aspects of the industry, including system requirements, manufacturing processes, circuit design, and simulation tools and test, greatly enhancing developers’ abilities to innovate and advance a wide range of technological applications.”