Intel talking about the ‘innovation’ of putting the CPU on top of a cache die in 2023

uk.pcmag.com

uk.pcmag.com

Bad luck, Intel.

From what they said about Arrow Lake before launch, I think they acknowledged the advantage of AMD’s vcache. They must know that they are in deep trouble, without their own version of the tech, to compete. I think we could see it on roadmaps soon, as a refresh, or as part of the same series as Arrow Lake.

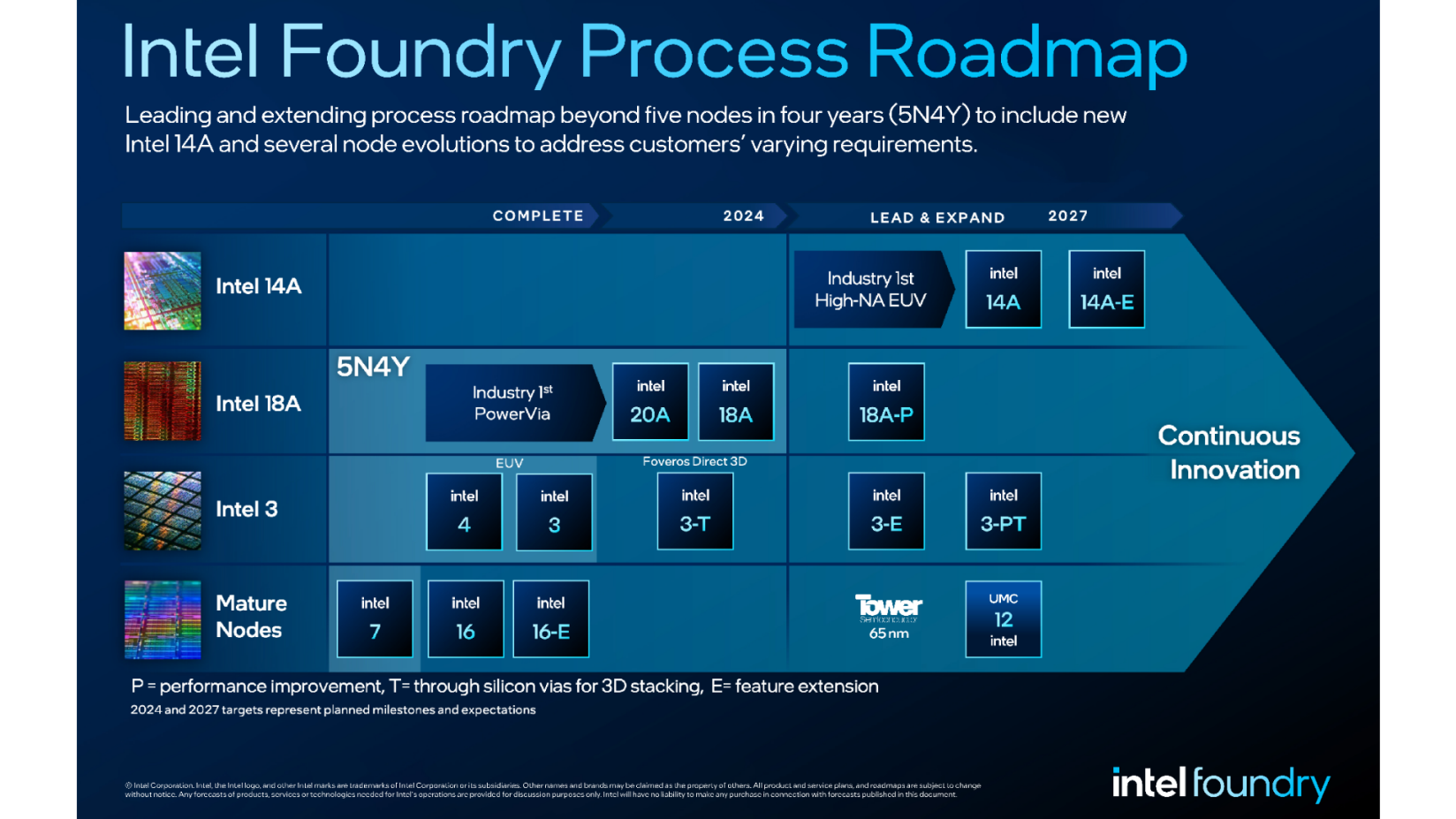

EMIB and Foveros are technologies already used in Arrow Lake, as discussed here:

https://www.muycomputer.com/2024/10...k-a-vista-de-silicio-todo-lo-que-debes-saber/

Intel has no plans to use a 3D V-cache-like technology on the company’s Meteor Lake processors, which start rolling out in December. “But in our roadmap, you’re going to see this idea of the 3D silicon, where we’ll have cache on one die, right? And then we’ll have CPU compute on a stacked die, on top of it,” Gelsinger said.

That sounds different than AMD, which has been using the chip-stacking tech to place added memory on top of its CPU dies. According to Gelsinger, Intel wants to do the opposite and stack the CPU on top of the memory.

Although Intel’s CEO was light on details, he said the company plans on connecting the chip dies vertically using its EMIB and Foveros processes, allowing the silicon to communicate together in a single package.

Intel: Our 3D V-Cache Tech Will Take a Different Approach Than AMD

The company plans to use the chip-stacking tech for Intel processors and offer it to third-party customers contracting with Intel's foundry business.

Bad luck, Intel.

From what they said about Arrow Lake before launch, I think they acknowledged the advantage of AMD’s vcache. They must know that they are in deep trouble, without their own version of the tech, to compete. I think we could see it on roadmaps soon, as a refresh, or as part of the same series as Arrow Lake.

EMIB and Foveros are technologies already used in Arrow Lake, as discussed here:

https://www.muycomputer.com/2024/10...k-a-vista-de-silicio-todo-lo-que-debes-saber/

Last edited: