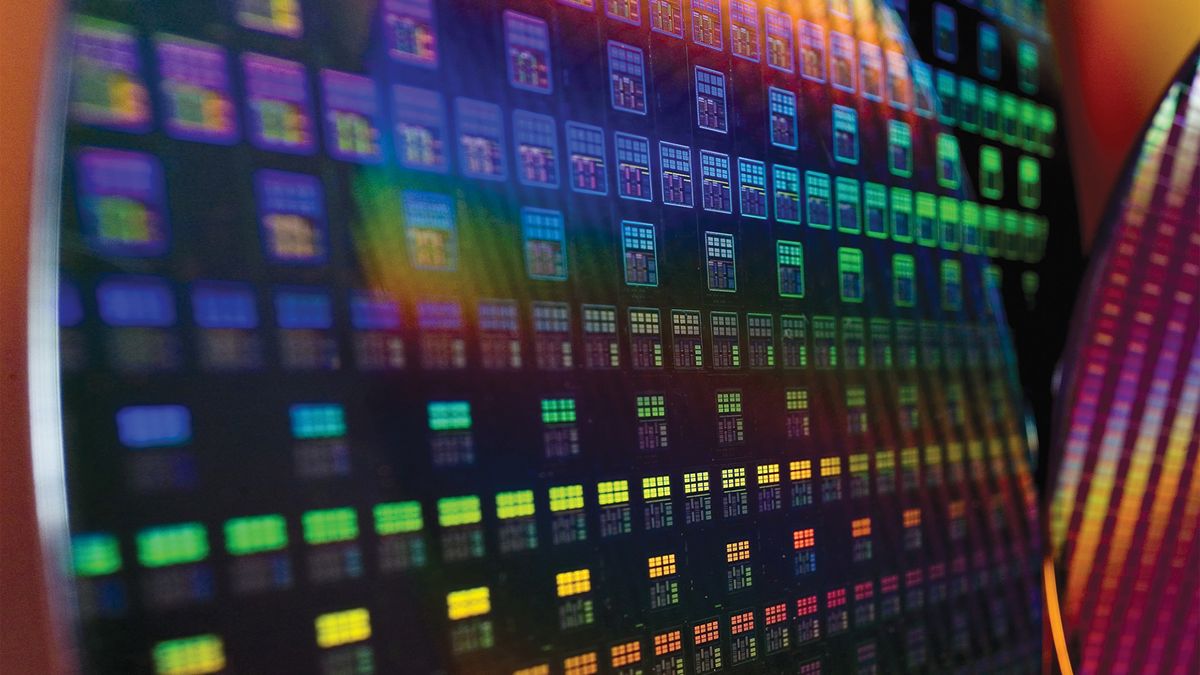

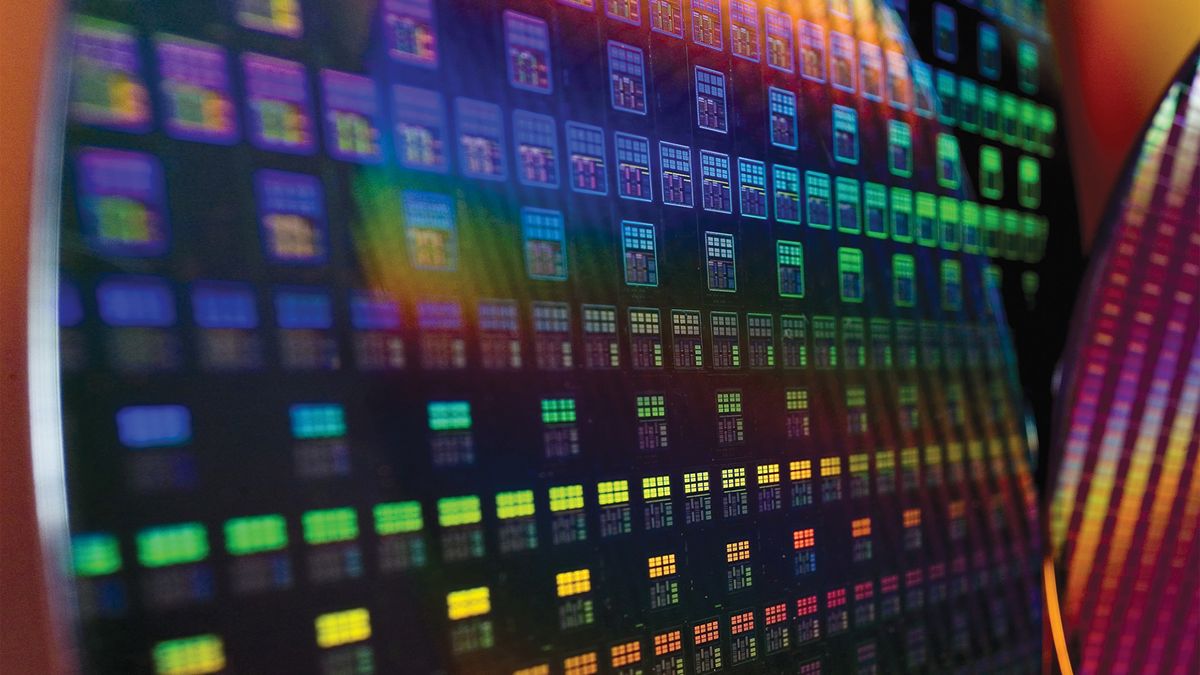

As described by the below Toms Hardware article, memory chips used as Cache in CPUs have basically stoped scaling. For example TSMC's next Gen 3nm node only has a 5% improvement over 5nm, Intel's 4 isn't better.

This matters because there is a recent trend of cache amount on CPUs rapidly scaling and the amount of power required and heat output of the memory is also rapidly increasing.

This causes complications for chip design because going forward more and more of desktop CPu space has to be allocated to cache as logic transistors get smaller but cache transistors stay the same size and adding more cache means more power draw and more heat and the alternative is simply having larger CPUs with more Chiplets

www.tomshardware.com

www.tomshardware.com

This matters because there is a recent trend of cache amount on CPUs rapidly scaling and the amount of power required and heat output of the memory is also rapidly increasing.

This causes complications for chip design because going forward more and more of desktop CPu space has to be allocated to cache as logic transistors get smaller but cache transistors stay the same size and adding more cache means more power draw and more heat and the alternative is simply having larger CPUs with more Chiplets

TSMC's 3nm Node: No SRAM Scaling Implies More Expensive CPUs and GPUs

Big problems from tiny memory cells.

Last edited: