-

Competitor rules

Please remember that any mention of competitors, hinting at competitors or offering to provide details of competitors will result in an account suspension. The full rules can be found under the 'Terms and Rules' link in the bottom right corner of your screen. Just don't mention competitors in any way, shape or form and you'll be OK.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Alder Lake-S leaks

- Thread starter Grim5

- Start date

More options

Thread starter's postsWho on earth games at 720p

Aslo a pointless exercise when gaming is a light load, one uses about 50 Watts, the other uses about 50 Watts...... lets turn that in to a slide to detract from the 250 Watts + ADL is using when editing and rendering your gaming adventures for YouTube.....

No one games at 720p with a top end GPU but it is a method to test cpu gaming potential.

Which becomes less and less relevant as the resolution increases. Gaming performance on archaic resolutions really is a pointless metric these days.

Soldato

- Joined

- 14 Aug 2018

- Posts

- 3,572

You're just as bad as Jigger with your distorted/exaggerated claims. No Intel have NOT smashed it all around. They've done well in many aspects but definitely not 'smashed it all around'.Agreed, very solid reviews, Intel have smashed it all around. Looking forward to tinker with mine!

I remember you banging on about how great/important AVX512 will be but yet we see here with ADL that you have to disable E-Cores to use AVX512. So much for that then.... So please stop with the predicting how great all things Intel will be with the distortions and hyperbole. I'm sure I am not the only one that finds it tiresome.

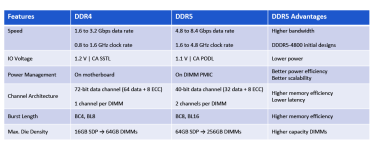

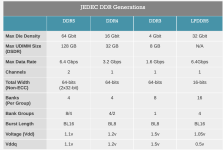

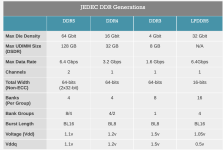

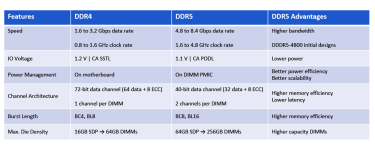

No, that's channels. Literally. Use Google:

https://techxplore.com/news/2020-07-ddr5-sdram-standard-boost-dual-channel.html

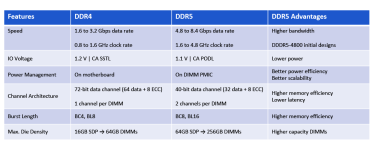

>> Each DIMM can handle two 32-bit memory channels instead of only a single 64-bit channel. Since each bank operates independently of each other, the burst length can be doubled and greater efficiency can be achieved. That means, for instance, DDR5 SDRAM can perform two 64-byte operations in the same time it takes DDR4 SDRAM to perform just one operation

In case you weren't aware, this was a huge bottleneck in multithreaded FP operations in all DDR4 systems.

So yeah, not the same thing as dual rank, "mate"

I know difference between Ranks and Channels. I think you need to go read up.

Also I work in I.T and know the difference for at least 40 years

.

.DDR5 has taken the 64bit channel and turned it into 2 x 32bit.. reality is it is not a true dual channel 64bit each channel (true dual channel would be 2 x 64bit), all they did was half it and tried to make it more efficient.

ADL is still a Dual channel platform/cpu.

https://blog.logicalincrements.com/2019/09/ram-channels-explanation-guide/

Last edited:

I'd like to see these power locked to 105 watts like top end Ryzen. Even 125w or 140w. If they used the same power settings as Ryzen these would show quite poorly. Intel are wringing the neck out of their nodes and people are not noticing.

The area behind Tom’s Diner in CP2077 is the most CPU intensive area in the game even at 4K due to the crowds of NPCs the game spawns in these areas. Yet HUB and the other reviewers only benchmark this game in the City center district where there are hardly any NPCs and the load on CPUs is reduced.If you have the, try Cyberpunk 2077 or WD:L with raytracing maxed out and 100% detail in WD:L, but DLSS ultra performance, and go to an actual in-game area and drive around (say Japan Town in CP, and Westminster for WD:L). Curious to see results.

No, that's channels. Literally. Use Google:

https://techxplore.com/news/2020-07-ddr5-sdram-standard-boost-dual-channel.html

>> Each DIMM can handle two 32-bit memory channels instead of only a single 64-bit channel. Since each bank operates independently of each other, the burst length can be doubled and greater efficiency can be achieved. That means, for instance, DDR5 SDRAM can perform two 64-byte operations in the same time it takes DDR4 SDRAM to perform just one operation

In case you weren't aware, this was a huge bottleneck in multithreaded FP operations in all DDR4 systems which made bandwidth utilisation very inefficient on non-server grade platforms.

So yeah, not the same thing as dual rank, "mate"

To add:

AnandTech said:In the desktop space, we’re used to one memory module having memory for one 64-bit memory channel. That’s true for DDR4, DDR3, DDR2 etc, but the DDR5 specifications move to 32-bit memory channels. So while each DDR5 module is still using 64-bits of bandwidth, there are technically two 32-bit memory channels worth of memory on each module. This can create a little bit of confusion, because it means that Intel 12th Gen, while still a 128-bit memory interface as previous generations, it uses 4x 32-bit channels, not 2x 64-bit. Undoubtedly companies (even Intel) still call this dual-channel, as a channel is usually inferred to be a 64-bit interface.

There is no easy solution here. 2DPC (two modules per channel) doesn’t really mean much if technically channel there infers 64-bit but you’re running on a 2x32-bit channel system. Some users are calling a DDR5 module a ’channel’ with two 32-bit ‘sub-channels’, although that is more a twisting of reality, given that sub-channels are often something else in memory design. Because we’ve used the word ‘module’ to imply a 64-bit channel for so long, and because memory can be installed with more than one module per 64-bit channel.

Source

So yes dual channel per DIMM but also no, not really

I'd like to see these power locked to 105 watts like top end Ryzen. Even 125w or 140w. If they used the same power settings as Ryzen these would show quite poorly. Intel are wringing the neck out of their nodes and people are not noticing.

I noticed, the P cores are also 3X the size of Zen 3 cores. Its just an incredibly inefficient architecture, comparatively, against an old CPU on an old node.

Associate

- Joined

- 11 Jun 2021

- Posts

- 1,024

- Location

- Earth

You're just as bad as Jigger

No need for that, I think you owe him an apology.

You're just as bad as Jigger with your distorted/exaggerated claims. No Intel have NOT smashed it all around. They've done well in many aspects but definitely not 'smashed it all around'.

I remember you banging on about how great/important AVX512 will be but yet we see here with ADL that you have to disable E-Cores to use AVX512. So much for that then.... So please stop with the predicting how great all things Intel will be with the distortions and hyperbole. I'm sure I am not the only one that finds it tiresome.

It's funny I know who you're replying to without even looking, dave the intel bot.

I know difference between Ranks and Channels. I think you need to go read up.

Also I work in I.T and know the difference for at least 40 years

You clearly weren't aware of the difference, and confused DDR5's dual channel per DIMM with dual-rank. I'm very well versed in computer architecture. It is you who needs more reading:

From Anandtech:

https://www.anandtech.com/show/1591...sed-setting-the-stage-for-ddr56400-and-beyond

>> The big change here is that, similar to what we’ve seen in other standards like LPDDR4 and GDDR6, a single DIMM is being broken down into 2 channels. Rather than one 64-bit data channel per DIMM, DDR5 will offer two independent 32-bit data channels per DIMM (or 40-bit when factoring in ECC). Meanwhile the burst length for each channel is being doubled from 8 bytes (BL8) to 16 bytes (BL16), meaning that each channel will deliver 64 bytes per operation. Compared to a DDR4 DIMM, then, a DDR5 DIMM running at twice the rated memory speed (identical core speeds) will deliver two 64-byte operations in the time it takes a DDR4 DIMM to deliver one, doubling the effective bandwidth.

If you insist on being wrong so be it. But hopefully your 40 years of IT experience will help you understand that on this, you're simply wrong. So man up and read up.

+1You're just as bad as Jigger with your distorted/exaggerated claims. No Intel have NOT smashed it all around. They've done well in many aspects but definitely not 'smashed it all around'.

I remember you banging on about how great/important AVX512 will be but yet we see here with ADL that you have to disable E-Cores to use AVX512. So much for that then.... So please stop with the predicting how great all things Intel will be with the distortions and hyperbole. I'm sure I am not the only one that finds it tiresome.

Congratulations for having 30 years of redundant information.I know difference between Ranks and Channels. I think you need to go read up.

Also I work in I.T and know the difference for at least 40 years.

DDR5 has taken the 64bit channel and turned it into 2 x 32bit.. reality is it is not a true dual channel 64bit each channel (true dual channel would be 2 x 64bit), all they did was half it and tried to make it more efficient.

ADL is still a Dual channel platform/cpu.

https://blog.logicalincrements.com/2019/09/ram-channels-explanation-guide/

You clearly weren't aware of the difference, and confused DDR5's dual channel per DIMM with dual-rank. I'm very well versed in computer architecture. It is you who needs more reading:

From Anandtech:

https://www.anandtech.com/show/1591...sed-setting-the-stage-for-ddr56400-and-beyond

>> The big change here is that, similar to what we’ve seen in other standards like LPDDR4 and GDDR6, a single DIMM is being broken down into 2 channels. Rather than one 64-bit data channel per DIMM, DDR5 will offer two independent 32-bit data channels per DIMM (or 40-bit when factoring in ECC). Meanwhile the burst length for each channel is being doubled from 8 bytes (BL8) to 16 bytes (BL16), meaning that each channel will deliver 64 bytes per operation. Compared to a DDR4 DIMM, then, a DDR5 DIMM running at twice the rated memory speed (identical core speeds) will deliver two 64-byte operations in the time it takes a DDR4 DIMM to deliver one, doubling the effective bandwidth.If you insist on being wrong so be it. But hopefully your 40 years of IT experience will help you understand that on this, you're simply wrong. So man up and read up.

https://www.rambus.com/blogs/get-ready-for-ddr5-dimm-chipsets/

So you admit you were wrong and you're now confirming what I said? Good. Although you did go back and edited your old posts to make yourself look less clueless, but whatever.

Like I said, higher bandwidth, and more efficient bandwidth utilisation, which helped improve scaling of multithreaded memory intensive FP tasks in DDR5 compared to DDR4, as Anandtech said so in the review.

Soldato

- Joined

- 25 Sep 2009

- Posts

- 10,006

- Location

- Billericay, UK

Linus was pretty upbeat about Alder Lake but since then I've watch HUB and Level1Techs and my enthusiasm for Alder Lake at the high end has waned quite a lot when you look at the power draw numbers for the extra performance it brings. The i5 still looks promising.

Congratulations for having 30 years of redundant information.

Thank you, doesn't change the fact that ADL is a dual channel platform and cpu. How many memory slots are there on ADL max ? 4 ? .. so makes it dual channel. Same with Zen3... only difference is how ddr5 works internally not the cpu or platform. As I said and showed in the link many don't class it as a true dual channel memory as all they really did was half it and then created another channel, basically same amount of data but more efficent use of the ram.

https://blog.logicalincrements.com/2019/09/ram-channels-explanation-guide/#

Read the part that states

DDR5: Breaking the Status Quo?

If you’ve been keeping up-to-date on DDR5 memory, you may have seen mention of DDR5 RAM sticks (yes, each stick itself) having two memory channels. And what they’re saying is true, from a certain point-of-view. From my understanding, these “channels” aren’t like the memory channels described above, but still apply a similar (though not quite the same) concept on the stick-by-stick level.

Micron, one of the only three manufacturers of memory chips, describes this development as “essentially turning an 8-channel system as we know it today into a 16-channel system.” So what is going on here?

From what I can tell, it seems that each stick can work with two separate bunches of data, though it can’t be moving data from both bunches across the actual (physical, on-the-motherboard) channels at the same time. For example, a stick could be receiving data on one half, and be preparing to send data on the other half in the meantime. This is still a significant improvement in design over previous iterations of RAM like DDR4, though not quite as dramatic as it sounds at first. Reality is often disappointing; we’ll just have to wait and see if this turns out to actually be the case.

https://www.rambus.com/blogs/get-ready-for-ddr5-dimm-chipsets/

People keep talking about 'just' the performance increase if they're pro-intel and 'just' the power increase if they're pro-amd...

12600 v 5600x is about 4% worse for power per performance (ie efficiency) in multi thread, and 14% worse in single threaded.

https://www.techpowerup.com/review/intel-core-i5-12600k-alder-lake-12th-gen/20.html

12600 v 5600x is about 4% worse for power per performance (ie efficiency) in multi thread, and 14% worse in single threaded.

https://www.techpowerup.com/review/intel-core-i5-12600k-alder-lake-12th-gen/20.html