Apologies - lost internet after the storm then had a couple of crazy busy days afterwards...

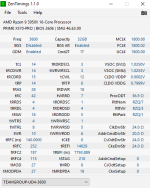

Anyway, thats a pretty good tune you have their already, there's not a huge amount more to gain I don't think. I take it from trdwr and twrrd being set to 18 and 7 that these are the 3600mhz 16-16-16 16gb sticks? It seems OCUK have tried to do something clever with the spd for Intel to auto set tRDWR and tWRRD without realising AMD doesn't work the same way. If you have XMP enabled, disable it and see if you can get board Auto values to load for those timings, they should be way lower. I'm not sure exactly how impactful they are, but they seem to be around double what I run with single sided. My (OLD!!) 16gb sticks ran these timings around 11 / 2 or 10 / 3 for whatever that is worth.

Aside from that minor faux pas caused by the SPD programming you can tighten up a couple of bits and pieces...

tRCDRW 8 should be possible on all B-Die

I haven't found B-Die yet that won't run tRP at least 1 below tCL, so you should be able to drop that to 13 or maybe even 12. That will allow you to reduce tRC and tRFC too.

tWR 10 will allow tRTP 5, however tWR 10 can work as a limit to your memory tune so make sure you test at 12 to see if you can further reduce more significantly impactful timings.

Tertiary timings:

Split your tertiary's into tRDRD based timings and tWRWR based timings. I have guessed at the meanings below, testing seems to back up my guesswork, but don't take these as gospel.

SCL's set Same Channel Latency (latency between channels - affects all setups using more than 1 stick)

SC if for Same Channel Different Dimm data transfers (latency between dimms if using two dimms per channel - affects 4 dimms setups only)

SD is for Same Dimm data transfers (latency between banks within the same dimm - affects double sided dimms only)

DD if for Different Dimm data transfers (latency between different dimms in different channels - affects all setups using more than 1 stick)

If you are using 2 x 8gb most of those timings wont be used so can be set to 1, with 4 x 8, 2 x 16 or 4 x 16 though you will need to explore your limits.

Method:

1) Reduce SCL's to minimum first. You'll usually find they both like being set to the same thing, SCL at 2 should be the target but may not be possible.

2) Once SCL's are minimised you can start reducing your RDRD and WRWR subtimings - you don't need to test these much, they should either be obviously unstable or fine. I reduce the lot by 1 and quick test each time. When I find instability I go back up to the last stable setting and start reducing the timings individually. Don't bother doing individual tuning of these timings from the start, it'll take ages.

I would try and aim for 3733mhz 1:1 if you can. 3800mhz IF booting means you are very close to stable - it probably just wants stupid voltage (so don't risk your 3950x trying). My cpu wont even post at 3800 IF yet 3733mhz is fully stable at reasonable volts. For reference, my voltage scaling with IF:

3200mhz 0.7vCCD, 0.7vDDG, 0.7vDDP (vSOC 1v stable @ 3200mhz)

3466mhz 0.775vCCD, 0.825vDDG, 0.8vDDP

3600mhz 0.825vCCD, 0.9vDDG, 0.9vDDP

3666mhz 0.825vCCD, 0.95vDDG, 0.925vDDP

3733mhz 0.85vCCD, 1.0vDDG, 0.95vDDP

vSOC I run at default (1.1v) with LLC set to mode 2 (2nd highest). Haven't needed to bump it on this 3900XT, though my earlier X cpus do need this voltage bumping to stop crackling audio at high IF. My 3800x for example requires 1.2vSOC for 3800mhz IF. 2 x 16gb may be harder on this voltage so I would probably do all the clocking at 1.2v then dial it down at the end.

If you want the final 0.5% once you have done all your other tweaking you can carefully test breaking the tRAS minimum rule. Go slowly as you can corrupt your hdd if you reduce tRAS/tRFC too low too quickly. Test for performance loss as well, things can get weird when breaking timing rules. I haven't been able to stabilise tRAS 21 (chipset minimum) yet, but tRAS 22 is stable on all my B-die at up to 3800mhz. This lets you pull tRC down to 36 and tRFC to 252 (or 216/220 if you can get down that low, but that's close to if not within corruption territory for 16gb dimms).

You have nearly all of your possible memory performance already, you're not leaving much on the table if you were to stop where you are now

.

GL dude

. I tend to lurk mostly and its only when something really piques my interest that I get tempted to post these days.

. I tend to lurk mostly and its only when something really piques my interest that I get tempted to post these days.