-

Competitor rules

Please remember that any mention of competitors, hinting at competitors or offering to provide details of competitors will result in an account suspension. The full rules can be found under the 'Terms and Rules' link in the bottom right corner of your screen. Just don't mention competitors in any way, shape or form and you'll be OK.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD Zen 3 (5000 Series), rumored 17% IPC gain.

- Thread starter AStaley

- Start date

- Status

- Not open for further replies.

More options

Thread starter's postsCaporegime

You're not 'Death'?? You mean Deaf

Is this argument over whether or not the zen2 chiplet design is inherently flawed?

Yes, apparently Zen is flawed. i would like to see him justify that argument.

Associate

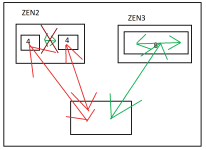

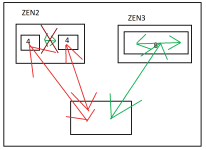

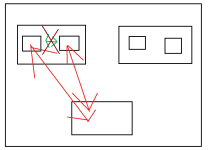

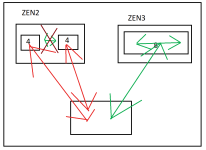

Nice paint job Zeed.

Although they have fixed the latency issue within the chiplet in Zen 3, where each core in a chiplet can now communicate to each other, without leaving the Chiplet to do so, with the likes of 5900x and 5950x, communication will still need to be transferred via the IO Die when communicating with each chiplet.

In an ideal world, if everything was housed in one chiplet, this would massively reduce latency. Maybe to come in future Zen... (But AMD did say, doing it with chiplets, and separate IO die makes it very cost friendly to mix and match new chiplets to test new vs old architectures on the same piece of silicone.

Although they have fixed the latency issue within the chiplet in Zen 3, where each core in a chiplet can now communicate to each other, without leaving the Chiplet to do so, with the likes of 5900x and 5950x, communication will still need to be transferred via the IO Die when communicating with each chiplet.

In an ideal world, if everything was housed in one chiplet, this would massively reduce latency. Maybe to come in future Zen... (But AMD did say, doing it with chiplets, and separate IO die makes it very cost friendly to mix and match new chiplets to test new vs old architectures on the same piece of silicone.

Last edited:

Permabanned

@mikeym @LtMatt gotta love informing idiots when they got no clue what they are talking about

@true_gamer added more so maybe with 1 brain cell he can comprehend difference between xen 2 and zen3 chiplets and where performance actuially came from and why its not as massive jump in multithread from zen2

@true_gamer added more so maybe with 1 brain cell he can comprehend difference between xen 2 and zen3 chiplets and where performance actuially came from and why its not as massive jump in multithread from zen2

Thats exacly why Zen3 is good in

ITS NOT MICROSOFT ITS FLAWED DESIGN only stupidity here is from You blaming microsoft for AMD's design decisions.

Do you understand why that design was XXXX now ?? Data inside Chiplet on ZEN2 is jumping over IO DIE not inside Chiplet adds extra latency adds heat reduces stability and so on.

Even if You force software to stik to using selected cores you are still gimped by this design.

Stupid like a fox maybe. TBH bolting clusters of 4 cores together over IF is also a stroke of genius. The alternative is a ring system and we have seen how that scales.

Permabanned

Hard to say man think it will be die aka all 8 cores some are hitting 5ghz on 5900xAnyone know if per core overclocking works on these chips?.

You could do it on Zen 2 with ryzen master but would cause some cores to just sit at base clock speed.

Caporegime

@mikeym @LtMatt gotta love informing idiots when they got no clue what they are talking about

@true_gamer added more so maybe with 1 brain cell he can comprehend difference between xen 2 and zen3 chiplets and where performance actuially came from and why its not as massive jump in multithread from zen2

Calm down Zeed, no need to go around calling anyone morons or idiots.

Soldato

TBF he seems quite upset. Chances of death >50%

Haha, poor Humbug. Getting some stick today. Hope he okay when I chat to him tonight.

Caporegime

Well done!

Any hints as to where you got it early? (whilst respecting the rules)

Here before its released - lol

Nice!

Caporegime

@Zeed Instead of drawing diagrams of what we all already know try actually explaining the reasoning behind your blanket statements. That would be the clever thing to do...

Caporegime

And gone... no need for this.

Associate

This explains it well with how Zen3 chiplet have been adjusted and how latency is vastly improved.

@mikeym @LtMatt gotta love informing idiots when they got no clue what they are talking about

@true_gamer added more so maybe with 1 brain cell he can comprehend difference between xen 2 and zen3 chiplets and where performance actuially came from and why its not as massive jump in multithread from zen2

This is wrong.

The CCD on Zen 2 has 2 quad-core CCX which talk to each other via the IF structure on their CCD, and not via the IO die which sits independently nearby:

https://hexus.net/tech/news/cpu/131549-the-architecture-behind-amds-zen-2-ryzen-3000-cpus/

Soldato

Going to jump all in with AMD this time around. Tomahawk, 5900X, 6900 XT. Its going to be a blast!

I'm thinking the same, though it'll be 5600X and 6800. More modest though it'll be a hell of an upgrade from my current machineGoing to jump all in with AMD this time around. Tomahawk, 5900X, 6900 XT. Its going to be a blast!

- Status

- Not open for further replies.