Whatever, he isn't at AMD now and how much they sustain the genius is pretty much case in point!

Its not all about one man, Keller put together a capable team before he left, they will continue on that genius.

Please remember that any mention of competitors, hinting at competitors or offering to provide details of competitors will result in an account suspension. The full rules can be found under the 'Terms and Rules' link in the bottom right corner of your screen. Just don't mention competitors in any way, shape or form and you'll be OK.

Whatever, he isn't at AMD now and how much they sustain the genius is pretty much case in point!

I didnt say it was but history isnt on the side of that suggestion, hopefully different this time!Its not all about one man, Keller put together a capable team before he left, they will continue on that genius.

I didnt say it was but history isnt on the side of that suggestion, hopefully different this time!

I have zero idea what this is supposed to mean, is abject market failure something deeper?With respect... Thats because you don't 'really know' what went on at AMD after Keller left.

It was a miss-judgement of where the market and technology was heading rather than AMD's execution of technology.

As far as AMD saw it the traditional X86 discrepancy between serial and parallel workloads was to become a thing of the past, applications would no long see it as one or the other but rather serial workloads would be instanced in parallel, A Heterogeneous System Architecture, The CPU would share its FP with the GPU, this was the purpose of Bulldozers modular design, they would simply be compute units, serial and parallel in the same package, 'APU's'.

AMD were wrong about where technology was heading, but the execution of the technology was genius, had it panned out for AMD things would be very different now.

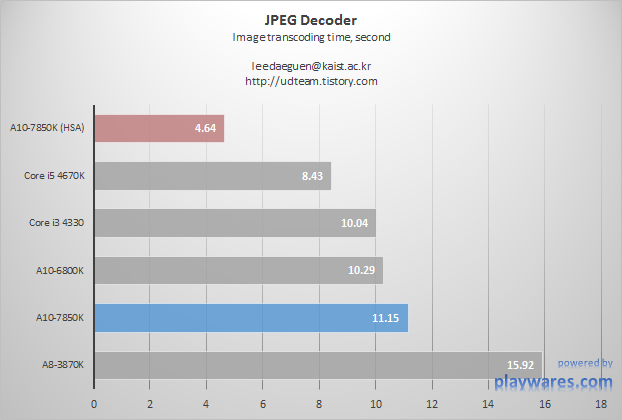

An example of HSA working in traditional X86 floating point workloads.... and Jim Keller had nothing to do with any of this.

As you can see, the technology had a profound impact, it worked.

AMD are a very clever bunch without Keller.

That roadmap is so out of date

Just to check. Are 4 ram sticks required for threadripper? (Is it needed to correctly fill all the memory channels and get optimal bandwidth?) Not messed with HEDT from either before, just pricing up.

Not required, but if you want the highest bandwidth, you want quad channel (4 or 8 sticks), but it will run in dual or single channel mode as well.

Threadripper is a 4 die EPYC CPU... there are 32 cores and 64 threads in them.

https://seekingalpha.com/article/41...c5d:815929faf6bebf7cde078bc1b54c4a88&uprof=55

24 core Threadripper incoming

Threadripper is a 4 die EPYC CPU... there are 32 cores and 64 threads in them.

https://seekingalpha.com/article/41...c5d:815929faf6bebf7cde078bc1b54c4a88&uprof=55

Not according to this article, threadripper and epyc are different, even down to the substrate.

https://www.overclock3d.net/news/cp..._on_the_threadripper_dummy_dies_controversy/1

To keep production cost down.Now they are saying they are not the same as EPYC, so why use a 4 dies package when you will only ever need two and why is the socket the same as EPYC?

It might not be as simple as that. It's possible that they intended to make "dummy dies" (which would have to include some circuitry anyway, it's not like it can be a blank slab of silicon) but didn't have time or something and decided to just use disabled real dies, at least to start with. Or it might be that the cost to make the dies is so low that putting in disabled ones is cheaper over say a year than the cost to developing and productionising "dummy dies".if you only ever intend to make a 2 die CPU them why make a more expensive 4 die CPU only to disable 2 of them? WTF?

To keep production cost down.

It might not be as simple as that. It's possible that they intended to make "dummy dies" (which would have to include some circuitry anyway, it's not like it can be a blank slab of silicon) but didn't have time or something and decided to just use disabled real dies, at least to start with. Or it might be that the cost to make the dies is so low that putting in disabled ones is cheaper over say a year than the cost to developing and productionising "dummy dies".

Does it really matter?

No, you're not fully addressing what i said, if AMD only ever intended to have a two die package CPU then why make a 4 die package?

AMD are trying to tell us its not EPYC, that's its different, so if its different then it has no use for the size of the thing and its very expensive 4096 pin TR4 socket, AMD are saying its a 2 die package.

So half the socket and its 4096 pins is useless, it has a figure of 8 Interposer... no one makes interposer's that shape.... if its intention was only ever to be a 2 die package then it would have been better and cheaper to design it as a 2 die package, not as a 4 die package apparently different to EPYC and then converted in a 2 die package with 2 dies added to it to hold up the far to big heat spreader. NO, of course not

Its an EPYC CPU that just didn't make the grade.