-

Competitor rules

Please remember that any mention of competitors, hinting at competitors or offering to provide details of competitors will result in an account suspension. The full rules can be found under the 'Terms and Rules' link in the bottom right corner of your screen. Just don't mention competitors in any way, shape or form and you'll be OK.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Intel Cannonlake, Cascade Lake, Ice Lake, Tiger Lake & Sapphire Rapid thread

- Thread starter TheF34RChannel

- Start date

More options

Thread starter's posts- Joined

- 12 Jul 2015

- Posts

- 1,694

The same as performance, architecture etc and yet you keep comparing them when suits you. What's the point of your comparison how fail for AMD is at 14nm, compared to intel's 10? I can have it on 50 and all that matters is performance, power draw etc.

I suspect you aren't talking to me?

- Joined

- 12 Jul 2015

- Posts

- 1,694

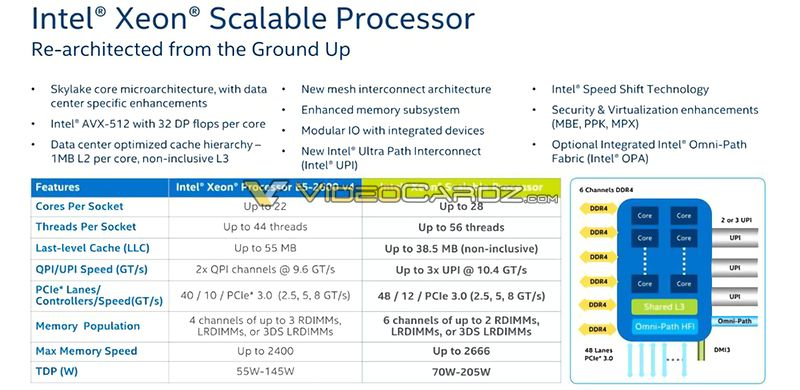

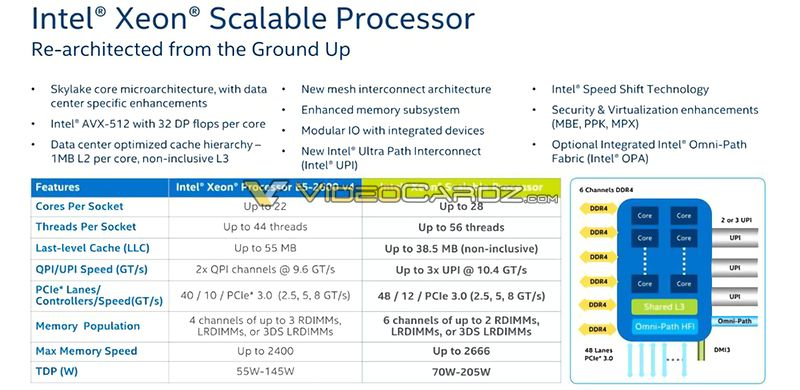

Xeon Scalable Processor “Skylake-SP” detailed

NDA ends today at 9:15 AM PDT. No comments, just slides.

More: https://videocardz.com/70874/intels-epyc-response-xeon-scalable-processor-skylake-sp

NDA ends today at 9:15 AM PDT. No comments, just slides.

More: https://videocardz.com/70874/intels-epyc-response-xeon-scalable-processor-skylake-sp

^^ was talking about some of that stuff in the TR thread and people insisting Intel would take 3-4+ years to catch up LOL.

Well Rroff, the 3-4+ years was clearly wrong. It looks like Intel will take much longer than that.

I'll just quote Marcelo Viana's post from that thread:

"Let's see i need 4 xeon processor to be able to beat a 1 amd epyc on pci-E lanes?

i need 2 xeon to be able to beat a 1 epyc on memory bandwidht right?

Also i need 2 xeons to be able to beat a 1epyc on number of virtual machines, or 4 xeons again to beat a dual epyc machine?

And if i decide that each of my virtual machines have 4cores/8 threads, i got 32ns of latency on epyc(because all 4 cores are on the same CCX) while on xeon i always have 100ns of latency because of this crap new mesh topology.

Also in order to xeons perform it must be overclocked, so it gonna be much more power hungry, while at other side the maximum tdp of epyc is 180W even with 32 cores."

Then of course there is the cost. I can't see any enterprise based users being even mildly impressed with this as Intel's response to AMD.

If that is truly the best response Intel can come up with, then they are going to be in serious trouble from now on in the server/data center market.

Well Rroff, the 3-4+ years was clearly wrong. It looks like Intel will take much longer than that.

Was meaning in terms of the technology i.e. developing a mesh system - the Skylake platform is **** but it will get refined on.

Was meaning in terms of the technology i.e. developing a mesh system - the Skylake platform is **** but it will get refined on.

The mesh system is not like Infinity Fabric FYI.

The slides they'd put out I wonder if they're intentionally meant to mislead and imply that. But they are not talking about multiple small dies on one package (EPYC).

They're talking about an improved method of stringing together multiple SOCKETS on one MOTHERBOARD. And also at the detriment of low-core inter-core latency.

It's not actually new information, it's just a mild extension to what you can see in Skylake-X.

They are not catching up with anything (yet).

The mesh system is not like Infinity Fabric FYI.

The slides they'd put out I wonder if they're intentionally meant to mislead and imply that. But they are not talking about multiple small dies on one package (EPYC).

They're talking about an improved method of stringing together multiple SOCKETS on one MOTHERBOARD. And also at the detriment of low-core inter-core latency.

It's not actually new information, it's just a mild extension to what you can see in Skylake-X.

They are not catching up with anything (yet).

Mesh and UPI (especially with regard to crossbar changes, etc.) have been designed for stringing together multiple cores in a variety of different scenarios - I think I linked to the older whitepapers in the TR thread - while they've not implemented something with the extensibility of IF none of it is particularly new to Intel.

No none of this is particularly new (aside from the flexibility of IF) to either Intel or AMD just iterating on developments that have been going on behind the scenes and/or used on Opteron, etc. in various iterations. People seem to think that IF is something that is revolutionary ground breaking from what AMD or Intel have done in the past and it isn't as much as they think compared to the background R&D both have had ongoing for years.

No none of this is particularly new (aside from the flexibility of IF) to either Intel or AMD just iterating on developments that have been going on behind the scenes and/or used on Opteron, etc. in various iterations. People seem to think that IF is something that is revolutionary ground breaking from what AMD or Intel have done in the past and it isn't as much as they think compared to the background R&D both have had ongoing for years.

True. But the question in my mind is "if that's the case, then why didn't Intel get going with it years ago" ?

I think the answer is fairly obvious................."we are the biggest, we are the best, we have no competition....................lets skrew them until they pop because it will cost us nothing"

Well, as it stands now some very very big "players" in the server and data center market have said "up yours Intel". One very very large "player" in the global laptop market has said the same. So Intel's decision to milk us until we pop may well become one of the worst decisions in corporate history.

Other than me deciding to buy channel tunnel shares in 1985 of course

AMD caught, probably more luck than judgement but who knows, Intel off cycle - too late for them to salvage things really this round but I doubt they will take it lying down on the next product cycle.

Generally there hasn't been the same need for it in the past - for instance node shrinks would make higher core counts, etc. on one die feasible and some areas of computing where its more useful have only really started to take off in more recent times.

Generally there hasn't been the same need for it in the past - for instance node shrinks would make higher core counts, etc. on one die feasible and some areas of computing where its more useful have only really started to take off in more recent times.

Xeon Scalable Processor “Skylake-SP” detailed

NDA ends today at 9:15 AM PDT. No comments, just slides.

More: https://videocardz.com/70874/intels-epyc-response-xeon-scalable-processor-skylake-sp

I counted 58 SKUs

http://www.anandtech.com/show/11544/intel-skylake-ep-vs-amd-epyc-7000-cpu-battle-of-the-decade/7

Maximum segmentation by Intel.

- Joined

- 12 Jul 2015

- Posts

- 1,694

I counted 58 SKUs

http://www.anandtech.com/show/11544/intel-skylake-ep-vs-amd-epyc-7000-cpu-battle-of-the-decade/7

Maximum segmentation by Intel.

I don't see the need for that many personally. Most of these won't sell a single one.

AMD caught, probably more luck than judgement but who knows, Intel off cycle - too late for them to salvage things really this round but I doubt they will take it lying down on the next product cycle.

Generally there hasn't been the same need for it in the past - for instance node shrinks would make higher core counts, etc. on one die feasible and some areas of computing where its more useful have only really started to take off in more recent times.

Who designed Ryzen? So no, it wasn't luck at all.

Who designed Ryzen? So no, it wasn't luck at all.

Not sure what you mean - he is a design engineer not a product strategist (not to discount any capabilities there).

Jim Keller... yeah, Intel really should have known better, this is not the first time Jim Keller working for AMD made Intel look almost second rate.Who designed Ryzen? So no, it wasn't luck at all.

AMD knew they couldn't compete with Intel in the data-centre space because they don't have the infrastructure to make huge dies cheaply.

Infinity Fabric was no accident, it was very much planed and successfully executed.

Seems he quite clearly meant the timing of the release of the new AMD chips not that they accidentally designed them. Intel are already committed to their current strategy and it will take time to respond to AMD and mid cycle can't just ditch their current designs to out engineer AMD.

Seems he quite clearly meant the timing of the release of the new AMD chips not that they accidentally designed them. Intel are already committed to their current strategy and it will take time to respond to AMD and mid cycle can't just ditch their current designs to out engineer AMD.

Yup they caught Intel at the moment they were least able to respond, won't discount it as an intentional strategy but that is far easier said than done and 9 times out of 10 more luck than judgement. Which has worked out pretty sweet for AMD.

Intel knew AMD hired Jim Keller 5 years ago and didn't react

https://thenextweb.com/insider/2012...chipmaker-amds-processor-group/#.tnw_mgMfWGNk

In fact , even a year ago, the CEO of intel is not interested in desktop. Intel wont have a `good` reply until 2019/2020 and until then will stuff more volts (or release xeon as desktop).

http://www.pcworld.com/article/3022...three-pillarsand-the-pc-isnt-one-of-them.html

https://thenextweb.com/insider/2012...chipmaker-amds-processor-group/#.tnw_mgMfWGNk

In fact , even a year ago, the CEO of intel is not interested in desktop. Intel wont have a `good` reply until 2019/2020 and until then will stuff more volts (or release xeon as desktop).

http://www.pcworld.com/article/3022...three-pillarsand-the-pc-isnt-one-of-them.html

Last edited:

What does Intel being caught with their pants down have to do with AMD's luck?

AMD designed a better product and Intel now have to up their game to catch up, that's it.

You don't get lucky in making better products, you very much plan to do that.

Luck doesn't come into it.

Intel in their arrogance may feel unlucky, because they didn't no one else can, and yet someone did..... unlucky!

AMD designed a better product and Intel now have to up their game to catch up, that's it.

You don't get lucky in making better products, you very much plan to do that.

Luck doesn't come into it.

Intel in their arrogance may feel unlucky, because they didn't no one else can, and yet someone did..... unlucky!

Last edited: