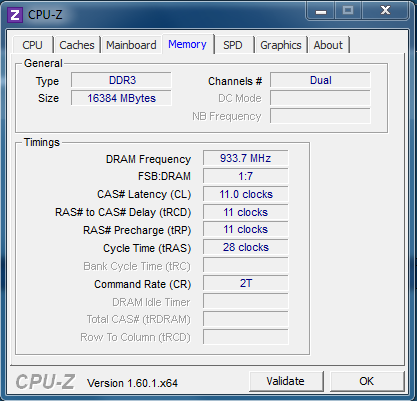

There are two timings that are linked together that will help greatly in overclocking. When these two timings are not set correctly, overclocking will not be as successful, and long-term stability can be hard to attain without excessive voltage. The above picture shows the primary and secondary timings we used to reach 2400 MHz with 1.575 V.

The two crucial timings, of course, are CAS Latency, and Write CAS Latency.

For CAS 6 and 7, tWCL should be CAS -1 (so CAS 6 gets tWCL 5 and CAS 7 gets tWCL 6)

For CAS 8 and 9, tWCL should be CAS -2 (so CAS 8 gets tWCL 6 and CAS 9 gets tWCL 7)

For CAS 10 and 11, tWCL should be CAS -3 (so CAS 10 gets tWCL 7, and CAS 11 gets tWCL 8)

I mention this as tWCL is not a timing that is talked about very often, if at all. However, because it has proven itself as a critical timing during testing, it is something that I felt must mention.

I have the Ivy Bridge i5 3570K.

I have the Ivy Bridge i5 3570K.